DE2-115 보드를 이용하여 LUT (Look-Up Table, Decoder, Memory) 를 실습한다.

[lut_8.v]

look-up Table (Decoder, Memory) 를 Verilog 로 기술한다.

더보기

/////----------------------------------------/////

module lut_8 (

input clk,

input rst_n,

input en,

input [2:0] addr,

output reg [7:0] dout

);

/////----------------------------------------/////

always @(posedge clk, negedge rst_n) begin

if (rst_n == 0) begin

dout <= 8'd0;

end

else begin

if(en == 1) begin

case (addr)

3'd0 : dout <= 8'b0000_0001;

3'd1 : dout <= 8'b0000_0010;

3'd2 : dout <= 8'b0000_0100;

3'd3 : dout <= 8'b0000_1000;

3'd4 : dout <= 8'b0001_0000;

3'd5 : dout <= 8'b0010_0000;

3'd6 : dout <= 8'b0100_0000;

3'd7 : dout <= 8'b1000_0000;

endcase

end

else begin

dout <= 8'd0;

end

end

end

endmodule

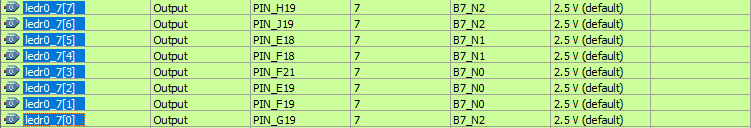

[Pin Assign]

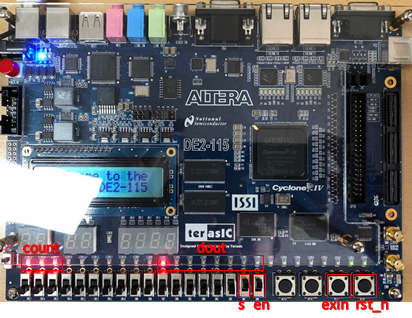

[Test Result]

이를 합성 후 출력결과를 학인하면 dout 이 LED 에 출력됨을 알 수 있다.

카운터 출력은 메모리 (ROM, LUT) 의 어드레스 신호이며, 어드레스에 따라 메모리의 값이 출력된다.

'원s > FPGA' 카테고리의 다른 글

| [DE2-115] Lab.4-1: Text LCD (0) | 2020.07.18 |

|---|---|

| [DE2-115] Lab.3-2: 7-segment Decoder (0) | 2020.07.12 |

| [DE2-115] Lab.2-3: Counter (0) | 2020.05.16 |

| [DE2-115] Lab.2-2: Counter (0) | 2020.05.16 |