DE2-115 보드를 이용하여 Text LCD 제어를 실습한다.

[Text LCD]

[ASCII Code]

[text_lcd.v]

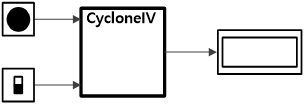

text lcd controller 를 Verilog 로 기술한다.

더보기

/////----------------------------------------/////

module text_lcd(

input clk,

input rst_n,

input en,

output lcd_en,

output lcd_rs,

output lcd_rw,

output lcd_on,

output [7:0] lcd_dout

);

reg [2:0] state;

reg [7:0] cnt;

parameter S0 = 0, S1 = 1, S2 = 2, S3 = 3, S4 = 4, S5 = 5;

/////----------------------------------------/////

always @(posedge clk, negedge rst_n) begin

if (rst_n == 0) begin

state <= S0;

cnt <= 8'd0;

end

else begin

cnt <= cnt + 1'b1;

case (state)

S0 : begin

if (cnt == 8'd70) begin

state <= S1;

cnt <= 8'd0;

end

end

S1 : begin

if (cnt == 8'd30) begin

state <= S2;

cnt <= 8'd0;

end

end

S2 : begin

if (cnt == 8'd30) begin

state <= S3;

cnt <= 8'd0;

end

end

S3 : begin

if (cnt == 8'd30) begin

state <= S4;

cnt <= 8'd0;

end

end

S4 : begin

if (cnt == 8'd16) begin

state <= S5;

cnt <= 8'd0;

end

end

S5 : begin

if (cnt == 8'd16) begin

state <= S4;

cnt <= 8'd0;

end

end

endcase

end

end

reg rs;

reg rw;

reg [7:0] dt;

////----------------------------------------/////

always @(posedge clk, negedge rst_n) begin

if (rst_n == 0) begin

rs <= 1'b0;

rw <= 1'b0;

dt <= 8'h00;

end

else begin

case (state)

8'h0 : {rs, rw, dt} <= {1'b0, 1'b0, 8'h00};

8'h1 : {rs, rw, dt} <= {1'b0, 1'b0, 8'h38};

8'h2 : {rs, rw, dt} <= {1'b0, 1'b0, 8'h0c};

8'h3 : {rs, rw, dt} <= {1'b0, 1'b0, 8'h06};

8'h4 : begin

case (cnt)

8'd0: {rs, rw, dt} <= {2'b00, 8'h80};

8'd1: {rs, rw, dt} <= {2'b10, 8'h41};

8'd2: {rs, rw, dt} <= {2'b10, 8'h6c};

8'd3: {rs, rw, dt} <= {2'b10, 8'h74};

8'd4: {rs, rw, dt} <= {2'b10, 8'h65};

8'd5: {rs, rw, dt} <= {2'b10, 8'h72};

8'd6: {rs, rw, dt} <= {2'b10, 8'h61};

8'd7: {rs, rw, dt} <= {2'b10, 8'h20};

8'd8: {rs, rw, dt} <= {2'b10, 8'h44};

8'd9: {rs, rw, dt} <= {2'b10, 8'h45};

8'd10: {rs, rw, dt} <= {2'b10, 8'h32};

8'd11: {rs, rw, dt} <= {2'b10, 8'h2d};

8'd12: {rs, rw, dt} <= {2'b10, 8'h31};

8'd13: {rs, rw, dt} <= {2'b10, 8'h31};

8'd14: {rs, rw, dt} <= {2'b10, 8'h35};

8'd15: {rs, rw, dt} <= {2'b10, 8'h20};

8'd16: {rs, rw, dt} <= {2'b10, 8'h20};

endcase

end

8'h5 : begin

case (cnt)

8'd0: {rs, rw, dt} <= {2'b00, 8'hc0};

8'd1: {rs, rw, dt} <= {2'b10, 8'h48};

8'd2: {rs, rw, dt} <= {2'b10, 8'h65};

8'd3: {rs, rw, dt} <= {2'b10, 8'h6c};

8'd4: {rs, rw, dt} <= {2'b10, 8'h6c};

8'd5: {rs, rw, dt} <= {2'b10, 8'h6f};

8'd6: {rs, rw, dt} <= {2'b10, 8'h20};

8'd7: {rs, rw, dt} <= {2'b10, 8'h57};

8'd8: {rs, rw, dt} <= {2'b10, 8'h6f};

8'd9: {rs, rw, dt} <= {2'b10, 8'h72};

8'd10: {rs, rw, dt} <= {2'b10, 8'h6c};

8'd11: {rs, rw, dt} <= {2'b10, 8'h64};

8'd12: {rs, rw, dt} <= {2'b10, 8'h21};

8'd13: {rs, rw, dt} <= {2'b10, 8'h20};

8'd14: {rs, rw, dt} <= {2'b10, 8'h20};

8'd15: {rs, rw, dt} <= {2'b10, 8'h20};

8'd16: {rs, rw, dt} <= {2'b10, 8'h20};

endcase

end

endcase

end

end

assign lcd_en = ~clk;

assign lcd_rs = rs;

assign lcd_rw = rw;

assign lcd_dout = dt;

assign lcd_on = en;

/////----------------------------------------/////

endmodule

[Pin Assign]

[Test Result]

이를 합성 후 출력결과를 학인하면 dout 이 LED 에 출력됨을 알 수 있다.

'원s > FPGA' 카테고리의 다른 글

| [DE2-115] Lab.5-1: UART transmitter (0) | 2020.07.25 |

|---|---|

| [DE2-115] Lab.4-2: ASCII Decoder (0) | 2020.07.19 |

| [DE2-115] Lab.3-2: 7-segment Decoder (0) | 2020.07.12 |

| [DE2-115] Lab.3-1: Look-up Table (0) | 2020.07.11 |