Combination Logic Simulation

조합 논리회로를 Verilog로 기술하고 Modelsim을 이용하여 시뮬레이션한다.

[2:1 MUX]

Module: mux2 는 s = 0 이면 y ≪ a, s = 1 이면 y ≪ b 를 출력하는 4 bits Multiplexer 를 assign 문으로 Verilog 로 기술한다.

|

|

Conditional and Logical Operator

| ? : | conditional |

| ! | negation |

| && | logical OR |

| || | logical AND |

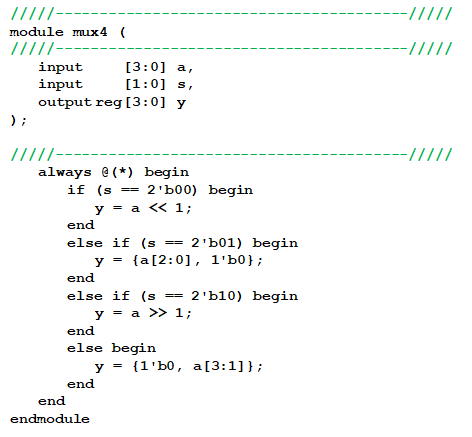

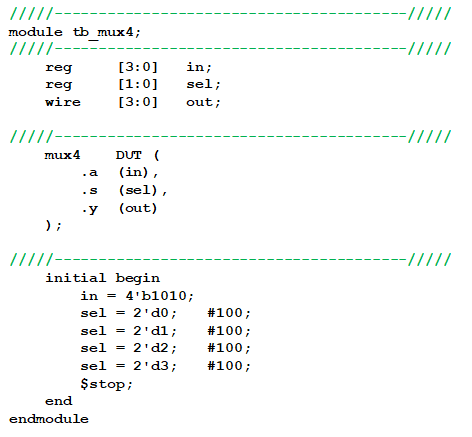

[4:1 MUX]

Module: mux4 는 2bits 제어신호 s 를 가지는 4 bits MUX 를 always 문으로 Verilog 로 기술한다.

mux4 에서 s = 0, 1 이면 오른쪽으로 1 bit 쉬프트 하고, s = 2, 3 이면 왼쪽으로 1 bit 쉬프트 한다. 쉬프트 연산은 Shift Operator 와 Concatenation Operator 로 기술할 수 있다.

|

|

* always @( ) 의 Event List 안에 Wildcard Operator: * 를 사용하여 else 문을 할당하여 의도하지 않은 Latch 생성을 방지한다.

Concatenation and Shift Operator

| { } | concatenation |

| {{ } } | replication |

| << | left shift |

| >> | right shift |

| >>> | signed reight shift |

[Decoder, Lookup table or ROM]

Module: lut8 는 always @(*) 와 case( ) 로 Verilog 로 Lookup Table 을 기술한다.

input: a 에 따라서 ouput: y 값이 결정된다.

|

|

* case( ) 문에 default 를 할당하여 Latch 가 발생하지 않도록 한다.

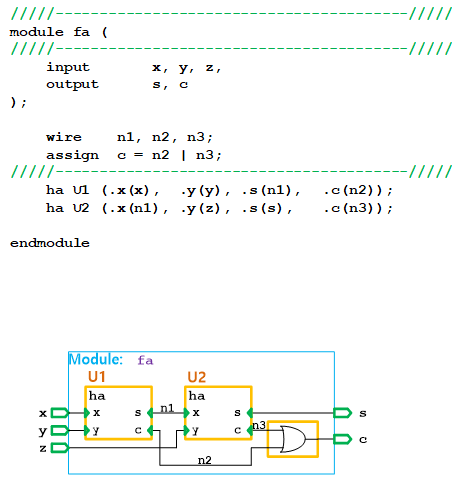

[Full Adder]

Module: fa 는 기술 된 ha 를 Instance 하여 Full Adder 를 Structual Level 로 기술한다.

|

|

* Structual Level Modeling 기술 시 Named port connecction 으로 기술한다.

'원s > Verilog' 카테고리의 다른 글

| [Verilog] Test Bench (0) | 2020.06.27 |

|---|---|

| [Verilog] Sequential Logic (0) | 2020.05.02 |

| [Verilog] Logic Gate (0) | 2020.03.21 |

| [Verilog] Data type (0) | 2020.03.08 |