Sequential Logic

순차논리회로를 기술하고 Modelsim을 이용하여 시뮬레이션 한다.

Register

[D flip-flop]

Module: dff4 는 4 bits d flop-flop 을 기술한다.

[Resettable register]

Module: dff4_v2 , dff4_v3 는 초기화 reset: rst_n 신호가 추가 한 d flop-flop 을 기술한다.

D flop-flop 의 dff4_v2 reset: rst_n 은 clk 에 동기되어 레지스터 출력: q 는 초기하 되며, dff4_v3 reset: rst_n 은 비 동기 되어 레지스터 출력: q 초기화 된다.

[Enabled register]

Module: dff4_v4 , dff4_v5 는 enable: en 신호가 추가 한 d flop-flop 을 기술한다.

[Shift register]

Module: dff4_v6 , dff4_v7 는 shift register 을 기술한다.

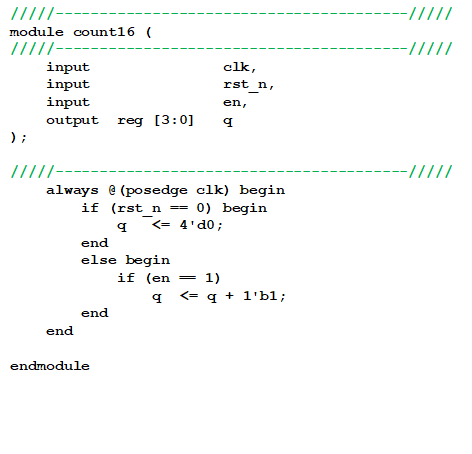

[Counter]

Module: count16 , count10 는 counter 을 기술한다.

반응형

'원s > Verilog' 카테고리의 다른 글

| [Verilog] Test Bench (0) | 2020.06.27 |

|---|---|

| [Verilog] Combination Logic (0) | 2020.04.05 |

| [Verilog] Logic Gate (0) | 2020.03.21 |

| [Verilog] Data type (0) | 2020.03.08 |